存储器数据通路实验

注:本项目与存储器应用实验二选一。

实验原理

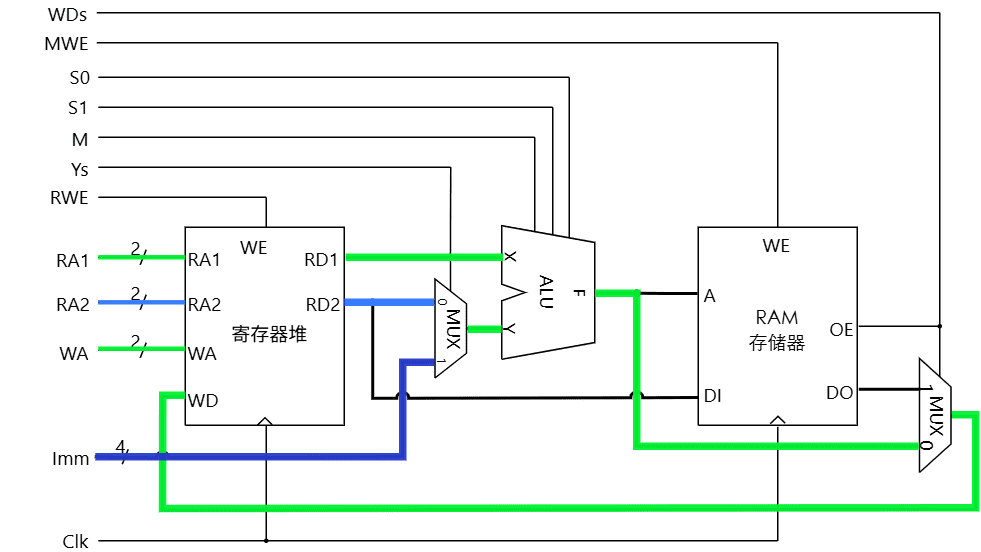

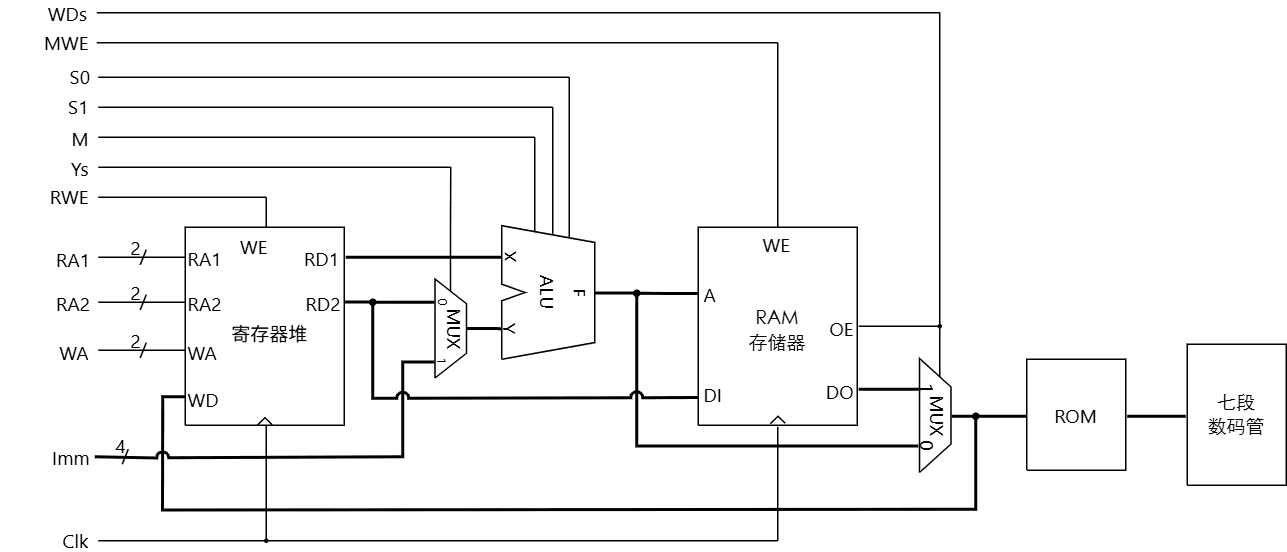

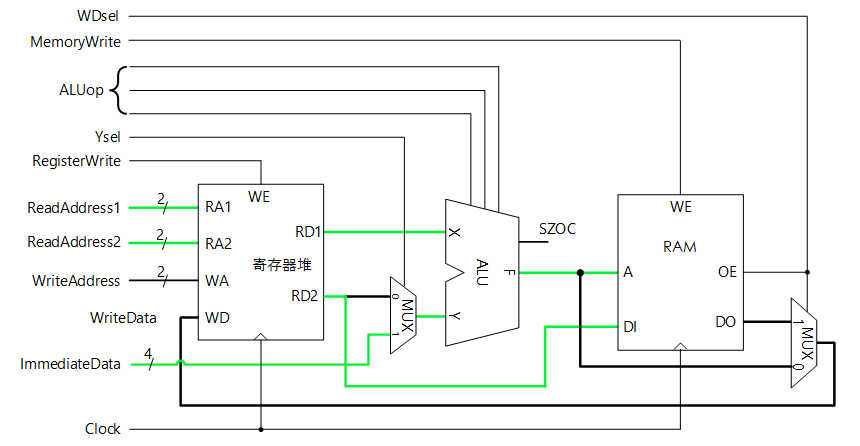

图 1是本实验的存储器数据通路,该数据通路使用了前面实验中的ALU、三端口寄存器堆和RAM、ROM存储器。 和运算器数据通路相比,运算部分基本没有变化,新增加了存储器。 DI是RAM的数据输入端口,写入RAM的数据由寄存器堆的RD2读端口提供。 RAM的地址A来自ALU运算结果F。 RAM的读出数据DO通过多路器连接到寄存器堆的写端口WD,可以写入寄存器堆。 ROM作为七段译码器,连接数码管显示WD端口的数值。

该电路可以将外部数据存入寄存器堆,进行ALU运算,以及在RAM和寄存器堆之间相互传递数据,下面从几个方面阐述工作原理。

存储器地址的产生

要对RAM读或写,必须要指定读写的RAM单元地址。 从图 1可知,RAM的地址A来自ALU的输出F,通常使用加法运算产生RAM地址。而加法的运算数据分别来自寄存器堆的RD1和立即数Imm,所以需要用RD1加上立即数来指定RAM的地址。从寄存器堆实验可知,RD1即RA1指定的寄存器的值。即

A = RD1 + Imm = R[RA1] + Imm

式中,R[n]表示编号为n的寄存器的值。

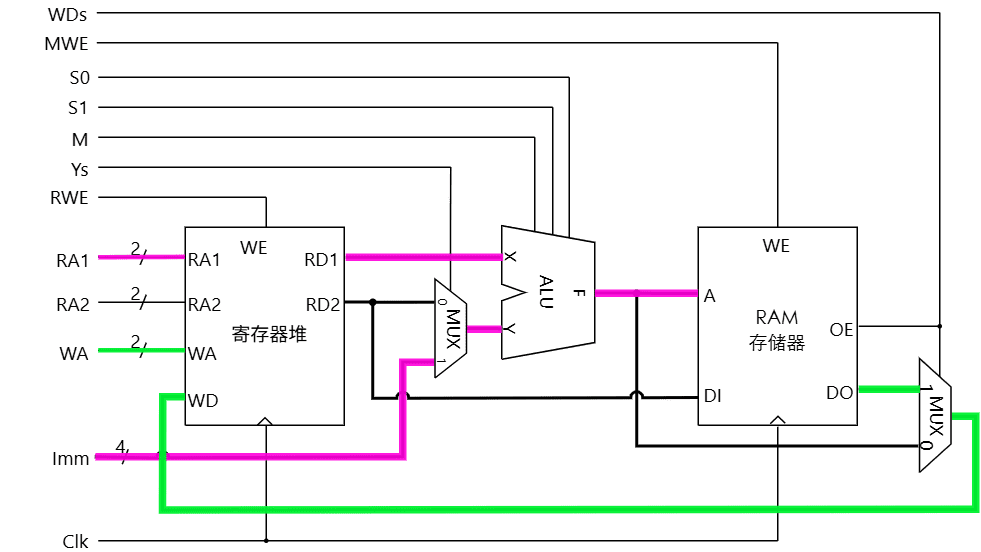

生成地址的信息路径如图 3红线所示。

特别地,如果RA1=0,即RD1为R0寄存器的值;根据寄存器堆实验的设计,R0寄存器的值恒为0,则

A = R[0] + Imm = Imm

同理,如果外部输入Imm=0,则

A = R[RA1]

实验任务

验证任务

依次完成以下验证任务,分析实验数据,判断结果的正确性。 若结果与预期不符,尝试分析故障现象并排除故障,提升分析问题与解决问题的能力。 最后保存仿真过程数据文件。

-

常数写入寄存器堆

从前面实验原理可知,RAM的地址需要寄存器参与运算后产生,写入RAM的数据也是来自寄存器堆。所以首先将2个不同的非零常数分别存入2个寄存器。

-

寄存器数据写入RAM

将前面已存入数据的2个寄存器的内容,一个与Imm相加作为RAM地址,另一个作为写入RAM的数据,完成RAM的写操作。

-

读出RAM数据并写入寄存器

将上面已经存入RAM的数据读出并写入空闲的其他寄存器。

| 分析结果时还应检查ROM输出的七段数据和数码管显示是否正确。 |

- 思考与拓展

-

如果需要将ALU运算结果存入RAM存储器,如何操作?