硬布线控制实验(RIM)

注:“RIM”表示控制器支持R型和I型运算指令以及M型访存指令。

实验原理

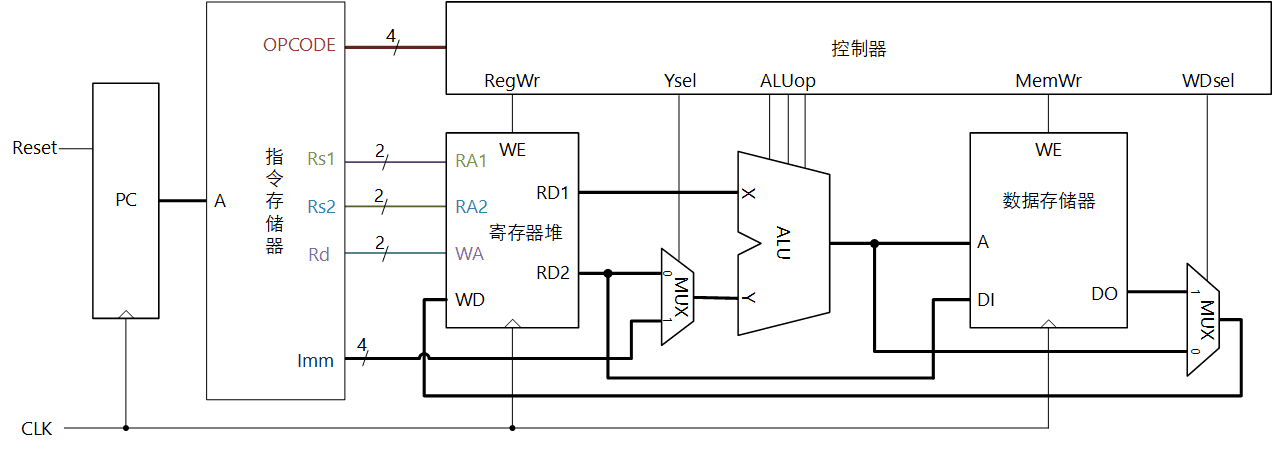

本项目是在支持运算指令的硬布线控制实验的基础上增加对存储器访问指令的支持。图 1给出支持运算和访存指令的原理框图,未支持分支指令。

图 1. 支持访存指令的数据通路及控制

图 1增加了如下控制信号:

-

数据存储器的写允许信号MemWr:为1时,当在CLK时钟上升沿到来,存储器执行写入操作。

-

多路器的选择信号WDsel:为0时,选择将ALU的运算结果送给寄存器堆的写数据端WD;为1时,将从存储器读出的数据送至WD。

下面分析存储器访问指令的执行。

根据指令编码表中关于load、store指令的功能描述,load指令将指定存储单元的内容装入指定寄存器,store将指定寄存器内容写入指定存储单元。 存储器的寻址采用变址寻址,变址寄存器号由rs1字段给出,偏移量由imm给出,所以有效地址EA=(rs1)+imm,即rs1指定的寄存器内容加上imm字段给出的偏移量作为有效地址。

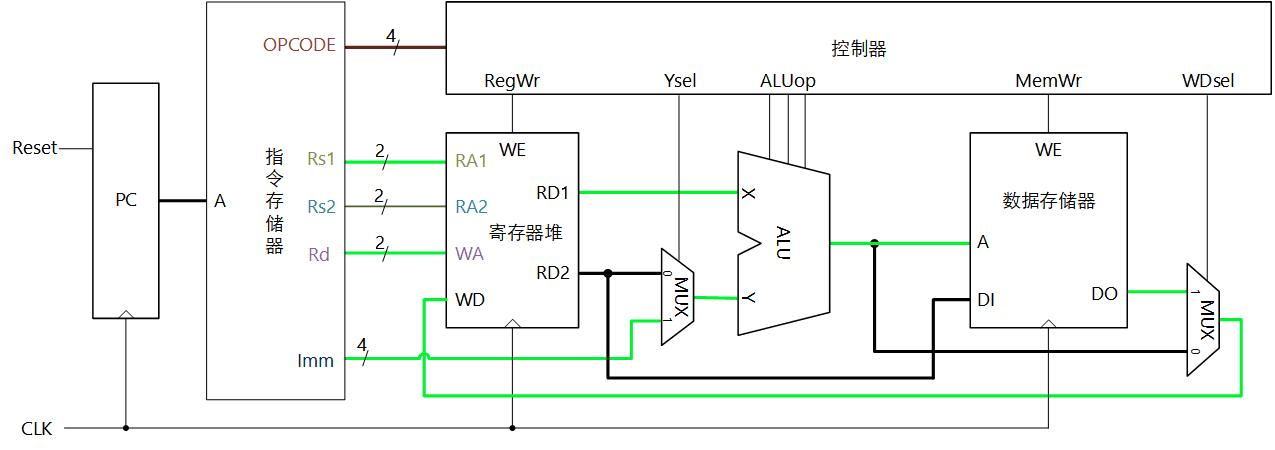

对于load rd, rs1, imm指令,从存储器读出的数据写入寄存器,寄存器号由rd给出。load指令的信息流示意图如图 2所示,绿色通路表示有效的信息流。根据信息流通路,读者可分析出控制信号的取值。

图 2. load指令的信息流示意图

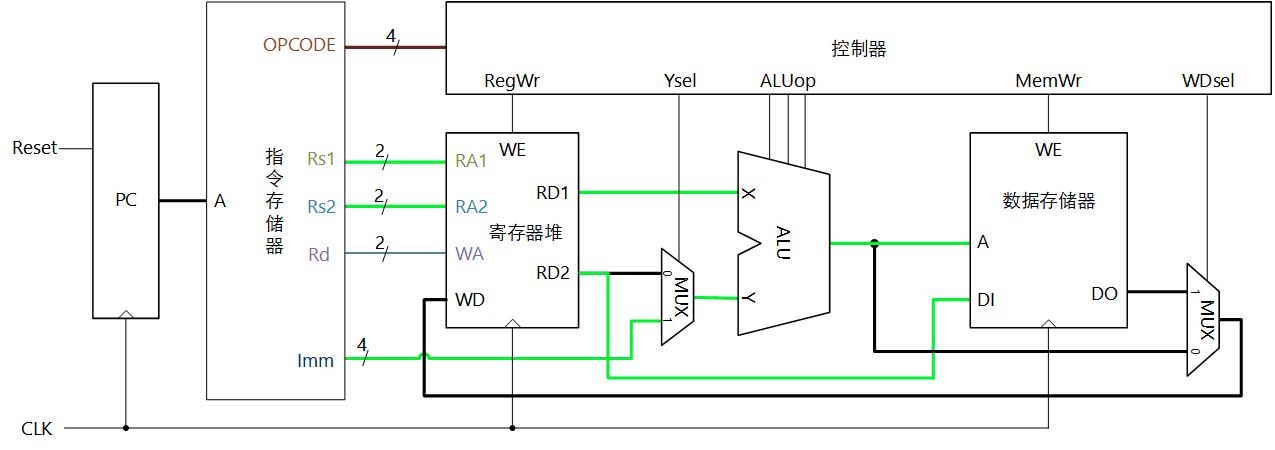

对于store rs2, rs1, imm指令,源数据的寄存器号由rs2给出,该寄存器的内容将被写入存储器。store指令的信息流示意图如图 3所示,绿色通路表示有效的信息流。根据信息流通路,读者可分析出控制信号的取值。

图 3. store指令的信息流示意图

实验任务

验证任务

-

仿真运行测试程序,分析运行结果

例 1给出了一个测试程序的例子。

例 1. 访存指令测试程序示例地址:机器指令 符号指令 0: 0x1815 addi r1, r0, 5 1: 0x202a ori r2, r0, 10 2: 0x09b0 sub r3, r1, r2 3: 0x3dc5 store r3, r1, 5 4: 0x3a10 load r1, r2, 0

符号指令翻译为机器指令的方法见硬布线控制实验(RI) 用测试程序初始化指令存储器。 根据指令功能对每条指令的仿真结果进行分析。如果运行结果与预期不符,应分析查找故障原因,例如控制器产生的控制信号是否正确。

-

验证更多指令(选做)

例 1测试程序只包含了部分运算指令,自己编写程序进行更全面的验证。