硬布线控制实验(RIB)

注:“RIB”表示控制器支持R型和I型运算指令以及B型分支指令。

实验原理

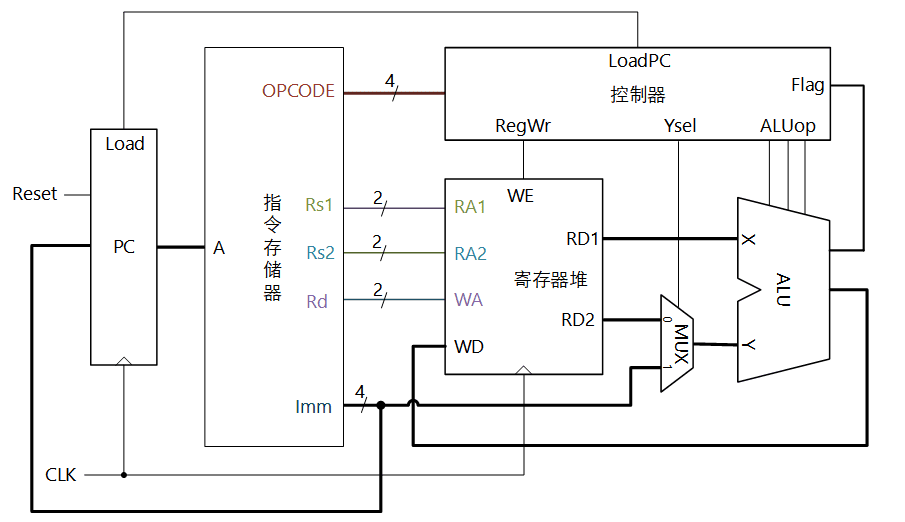

本项目是在支持运算指令的硬布线控制实验的基础上增加对分支指令指令的支持。原理框图如图 1。

由于程序转移需要修改程序计数器,和仅支持运算指令的硬布线控制实验的原理图相比,图 1的主要变化如下。

-

立即数传递路径

根据指令系统设计,转移地址由立即数imm提供。 所以,imm不仅可以作为运算数经多路器连接到ALU的Y输入端,也可作为转移地址送给PC。

-

程序计数器PC

程序计数器PC具有装数功能,由装数使能端口Load控制;在Clk上升沿到来时,如果Load为1,则将imm装入PC,实现程序转移;否则PC值加1,即顺序执行。

-

控制器

控制器输出增加了装数使能信号LoadPC,连接到PC的Load端口。LoadPC为1时,PC装载来自指令中的立即数imm;为0时,PC加1。 控制器的输入增加了ALU运算结果的特征标志,用于比较运算。

在硬布线控制实验(RI)中,已经练习了实现R型和I型运算指令的控制器的设计,基本方法是根据opcode译码产生数据通路上的各个控制信号,实现指令功能。对于B型分支指令,不仅要进行指令译码,还需要依据来自ALU的标志位判断是否产生转移控制信号。 下面举例说明支持分支指令的控制器设计方法。

以beq rs1, rs2, imm指令为例,该指令比较rs1和rs2寄存器的值是否相等,如果相等,则程序转移,下一条指令的地址由imm给出;如果不相等,则顺序执行。

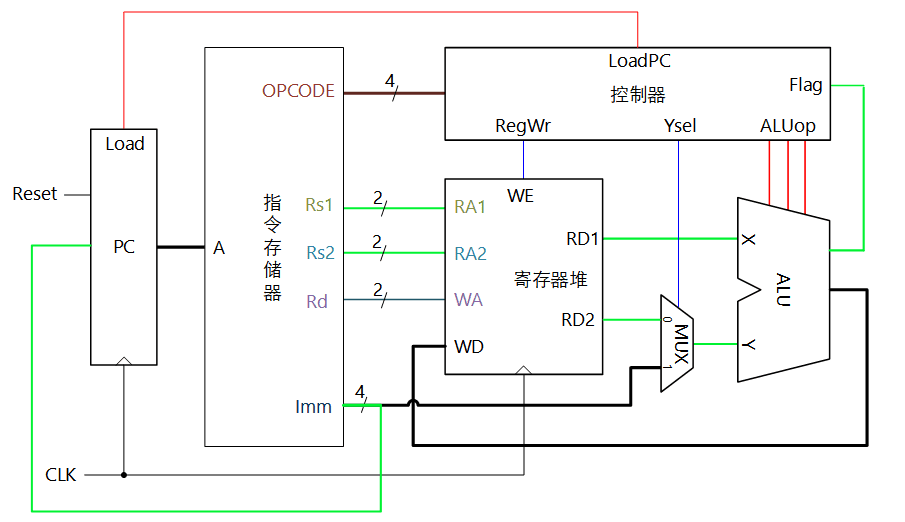

转移发生时分支指令的信息流如图 2所示,绿色通路表示有效的信息流,红色表示控制信号。

当转移发生时,控制信号LoadPC=1,将转移地址装入PC;如果不发生转移,LoadPC=0,PC加1。 可见,LoadPC并不是固定为1或为0,而是要根据比较运算的结果决定程序是否转移。所以,LoadPC不能单纯根据opcode产生。 opcode只能分辨是不是分支指令以及比较的类型,还需要与比较运算配合,才能产生控制信号。

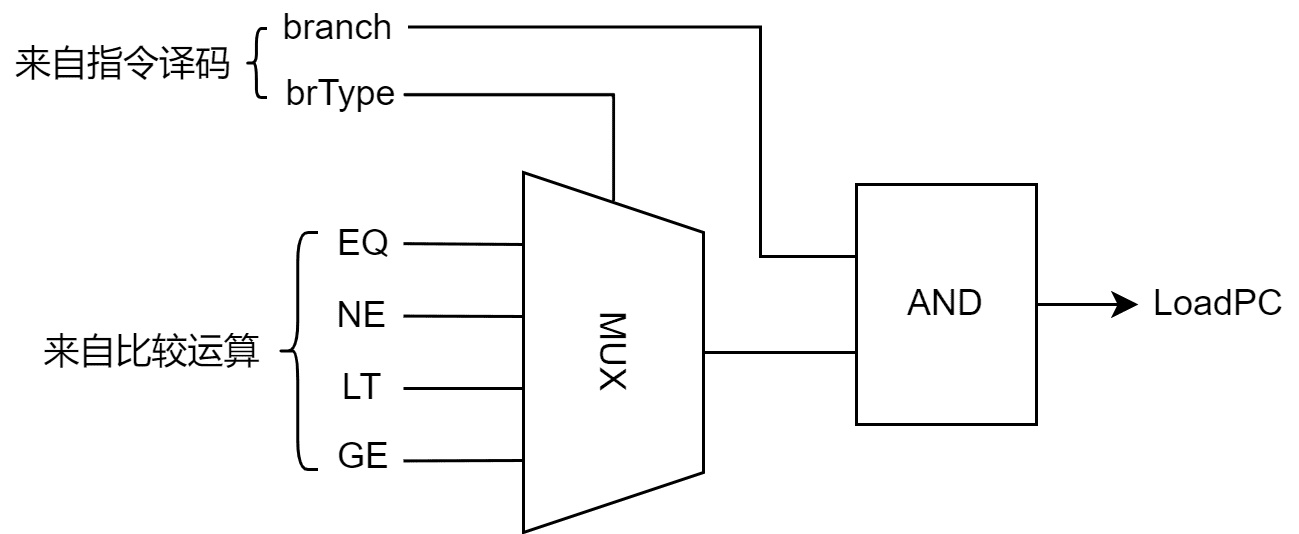

图 3给出了转移信号的生成方法。 其中比较器可以采用前面比较运算实验的电路,SF、ZF、OF、CF是来自ALU的运算结果特征标志,EQ、NE、LT、GE是比较的结果,分别表示相等、不等、小于、大于等于。 4选1多路器用来从4种比较结果中选择一个。2位的选择信号brType由指令译码根据分支指令的类型产生。 但是多路选择器MUX输出的信号并不能直接作为LoadPC信号,还要判断当前指令是不是转移指令。所以MUX的输出经过一个与门,由branch信号控制与门,如果不是分支指令,branch为0,则LoadPC为0;若是分支指令,branch为1,则将多路选择器的输出传递到与门输出作为LoadPC,也就是根据指令类型和比较结果决定程序是否转移。

表 1给出了beq指令的控制信号取值。

| 指令助记符 | opcode | Ysel | M | S1 | S0 | RegWr | branch | brType1 | brType0 |

|---|---|---|---|---|---|---|---|---|---|

beq |

0110 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

bne |

1011 |

||||||||

blt |

1100 |

||||||||

bge |

1101 |

|

依据标志位比较数的大小,ALU应进行减法运算。 |

实验任务

验证任务

-

仿真验证

因为控制器的作用是控制指令的执行,所以需要通过执行指令来检验控制器的设计。例 1给出了一个测试程序的例子。

例 1. 分支指令测试程序示例地址: 机器指令 符号指令 0: 0x1815 addi r1, r0, 5 1: 0x202a ori r2, r0, 10 2: 0x09b0 sub r3, r1, r2 3: 0x2ec0 bne r2, r3, 0

符号指令翻译为机器指令的方法见硬布线控制实验(RI) 用测试程序初始化指令存储器。 上面测试程序使用的指令种类有限,自己编写程序进行更全面的验证。

根据指令功能对每条指令的仿真结果进行分析。如果运行结果与预期不符,应分析查找故障原因,例如控制器产生的控制信号是否正确。

-

运行斐波那契数列计算程序(选做)

将概述(指令系统)中斐波那契数列计算程序的机器码作为ROM的数据。 仿真运行程序,验证结果是否正确。