运算器数据通路实验

实验原理

计算机本质上是一个加工处理二进制信息的电路,包括ALU、寄存器、存储器等部件,这些部件通过信号线以某种方式连接起来,并且在控制器的控制下,使信息按照一定的规则在各个部件之间有序流动,完成信息的加工处理。这些信息加工部件及信息传递路径的总和就称为数据通路。

不同结构的数据通路在成本、速度及工作方式上有着较大差异。 总体来说可以分为两种类型:多周期数据通路和单周期数据通路。多周期数据通路完成一次加法运算需要多个时钟周期(如3个周期),而单周期数据通路只需要一个时钟周期就可以完成一次运算处理。 虽然不能单纯以时钟个数的多少来评价性能的优劣,但从发展历史来看,单总线数据通路是早期技术的产物,当时的主要考量是减少连接线的数量、降低成本。 而现代处理器更关注性能,普遍采用流水线结构。 单周期数据通路更有利于演变为流水线结构,所以本实验只考虑单周期数据通路。

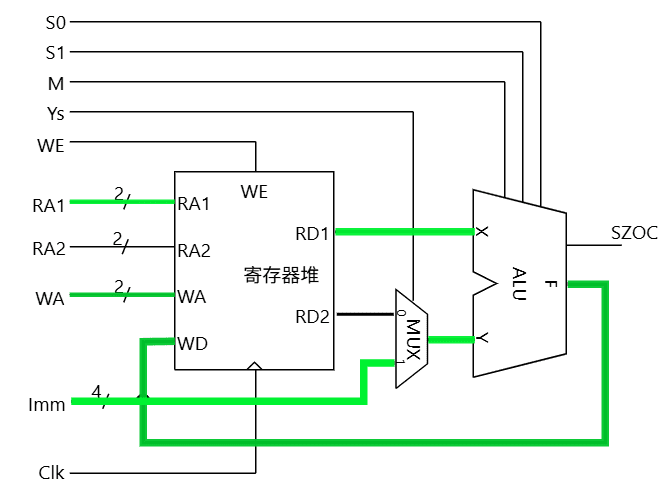

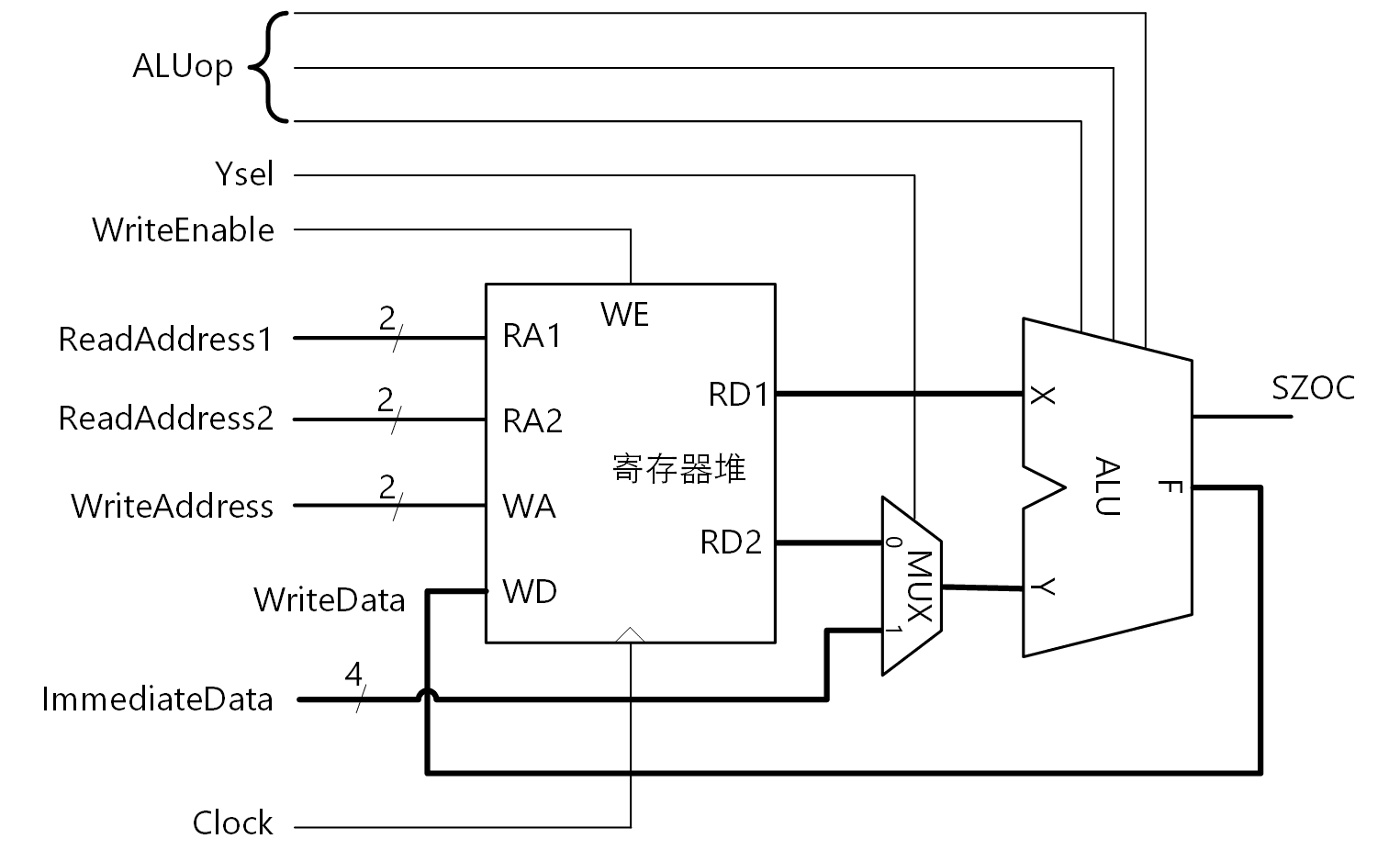

图 1是一个单周期数据通路的实例,使用了前面实验完成的ALU和三端口寄存器堆。 ALU输入端X的运算数据来自寄存器堆的RD1读端口,另一个输入端Y的运算数据可以来自寄存器堆的RD2读端口,或者来自立即数。 寄存器堆写端口WD的数据来自ALU的运算结果F。 该数据通路可以在一个周期内完成从寄存器堆读数据、ALU运算、运算结果保存到寄存器堆。

两个寄存器之间的运算

下面以两个寄存器间的运算为例,说明数据通路的信息加工过程。 两个寄存器间的运算关系可用下式表示。

R[WA] = R[RA1] op R[RA2]

式中,R[n]表示编号为n的寄存器的值,op表示ALU进行的运算。

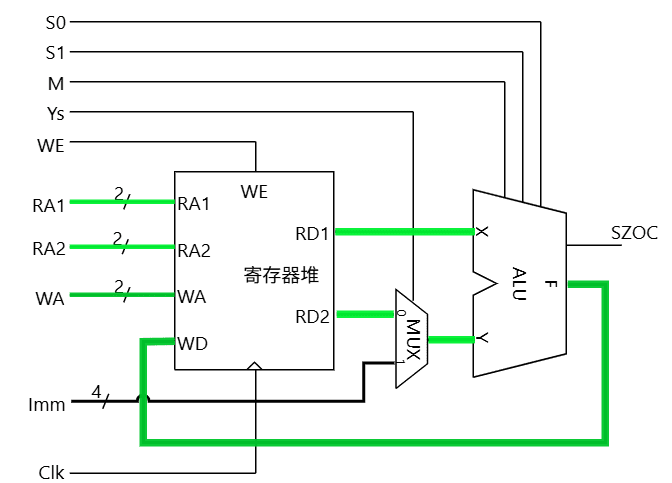

信息传递路径如图 2绿线所示。 两个寄存器的值分别从RD1和RD2读出,为此需要通过RA1和RA2提供寄存器号。 RD1直接连到了ALU的X输入端,但RD2和ALU的Y输入端之间还插入了一个2选1多路器。 因为RD2连接的多路器通道0,为了将RD2送到Y端,需要控制Ys为0,使2选1多路器选择通道0的RD2。 ALU的运算功能由M、S1、S0控制。运算结果F直接作为寄存器堆的写数据WD。 通过前面寄存器堆实验已经知道,为了将WD数据写入寄存器堆,需要提供欲写入寄存器的寄存器号WA,并且允许写入即WE为1,最后在Clk时钟上升沿的触发下将运算结果写入WA指定的寄存器。

实验任务

设计任务

用Digital仿真软件按照图 1绘制电路图。 数据通路的数据位数为4位。 ALU和三端口寄存器堆使用前面实验完成的。

|

必要时可调整子电路符号的宽度和端口顺序。相关操作参考层次化设计 - 子电路图形符号的外观。 |

验证任务

依次完成以下验证任务,分析实验数据,判断结果的正确性。 若结果与预期不符,尝试分析故障现象并排除故障,提升分析问题与解决问题的能力。 最后保存仿真过程数据文件。

|

为了能够观察到寄存器堆内部每个寄存器的输出,可开启「显示测量值表格」或「显示测量图」,动态显示可测量组件的当前输出值。 |

-

将非零常数存入寄存器

开始仿真后所有寄存器的值均为0,需要先向寄存器写入非零数据,才能进行后续的运算。 例如,假设要将常数9存入R2寄存器,则可将常数9通过Imm输入,与R0进行加法运算后结果存入R2寄存器,即完成

R[2]=R[0]+9=9。运算过程参考实验原理部分寄存器和立即数之间运算的特例。存入的常数应有助于后续步骤检验实验电路的功能和特性。 例如,应有助于验证数据通路可进行4位二进制运算,有助于检验运算结果的标志位等。

-

完成寄存器和立即数之间的运算并保存运算结果

将前面已存入数据的寄存器的内容,通过ALU与Imm给出的常数进行算术、逻辑运算,结果存入另一寄存器。 例如,假设前面已将R2存入数据,将其与Imm进行加法运算后结果存入R3寄存器,即完成

R[3]=R[2]+Imm。运算过程参考实验原理部分寄存器和立即数之间的运算。 -

完成两个寄存器之间的各种运算并保存运算结果

将前面已存入数据的2个寄存器的内容,通过ALU进行算术、逻辑运算,结果存入另一寄存器。 例如,假设R2、R3已经存有数据,进行加法运算后结果存入R1寄存器,即完成

R[1]=R[2]+R[3]。运算过程参考实验原理部分两个寄存器之间的运算。