译码器实验

实验任务

-

生成2-4译码器电路

学习电路生成,使用真值表生成带使能端的2-4译码器电路。

-

设计验证电路

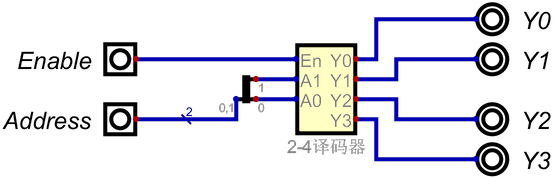

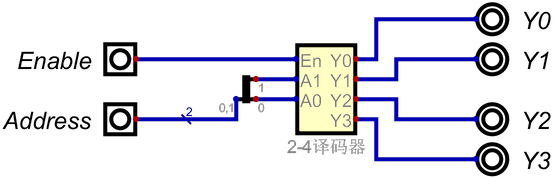

图 1. 包含子电路的译码器实验电路

图 1. 包含子电路的译码器实验电路 -

电路测试

例 1. 2-4译码器测试用例Enable Address Y3 Y2 Y1 Y0 repeat(4) 0 (n) bits(4, 0) repeat(4) 1 (n) bits(4, 1<<n)测试用例标题行的符号必须与电路图的输入输出组件的名称一致。

生成2-4译码器电路

学习电路生成,使用真值表生成带使能端的2-4译码器电路。

设计验证电路

电路测试

Enable Address Y3 Y2 Y1 Y0

repeat(4) 0 (n) bits(4, 0)

repeat(4) 1 (n) bits(4, 1<<n)| 测试用例标题行的符号必须与电路图的输入输出组件的名称一致。 |